Transaction Level Modeling (TLM) 是一種用來建立component和system的高度抽像模型的modeling style。在TLM中,資料(data)被表示為transaction(包含random、protocol特定資訊的class object),這些transaction透過TLM interface的連接埠流入和流出不同的component。

因為大量訊號與不同protocol相關。所以TLM帶來了更高層次的抽象,在現在的驗證環境中非常需要,如果我們能夠將資料和訊號變化表示為transaction(如寫入操作/讀取操作),那麼理解、調試和驗證就會比較好理解。

UVM提供了一組transaction-level的通訊接口,可用於component之間的連接,方便data packet可以在component之間傳輸。

這個設定的好處在於,一個元件與其他元件可以完全獨立,並提高了可重複使用性(reusability)和靈活性(flexibility),只需要不同元件之間都有 TLM interface可以傳輸資料即可。

1 | class simple_packet extends uvm_object; |

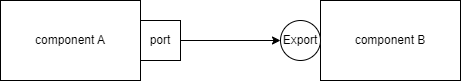

上面的 simple_packet object是一個transaction,透過TLM interface 連接埠port和export從component A 發送到component B。如下圖: