interface 是把訊號封裝進一個block的方法,把所有相關的訊號group在一起可以讓之後比較好重複使用,而且可以讓DUT和TB更容易串接起來。

連接到DUT的訊號一定support 4種state的signal,因為DUT的訊號可能會有0/1/X/Z四種state,如果是用bit的話就只會有2種state,所以必須要用可以代表4種state的logic

如果要指定interface裡面訊號的方向,可以用modport指定方向,下面的例子是以DUT的角度使用這個interface的話,DUT需要用enable和clk當作input,然後產生出data當output。

Example:

1 | interface busInterface(input clk); |

下面是使用interface的例子,例子裡面的DUT是一個簡單的design,會在posedge的時候trigger,如果訊號enable=1的話,會把data+1,不然就會把data清為0,並且DUT是使用interface當作參數。

Example:

1 | interface busInterface(input clk); |

這個例子沒有output,主要是要知道interface如何宣告和使用,例子裡面有用busInterface來create一個instance叫做busIf,輸入的參數是clk,然後DUT使用busInterface裡面的訊號,並且是使用modport DUT的input/output方向的訊號。

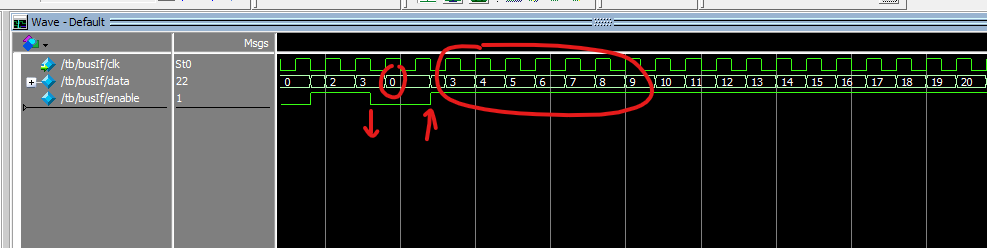

可以看到tb的initial block裡面的busIf.enable變動,DUT就會因為訊號變化所以會有相對應的動作,如下圖。